# A 5.8 GHz Fully-Integrated Power Amplifier for 802.11a WLAN System

G. C. Lin and Z. M. Lin

Abstract-In this paper, a 5.8 GHz fully-integrated power amplifier is designed and implemented in a 0.18-µm radio frequency CMOS process. The power amplifier is formed by a cascaded class-D pre-amplifier and a class-E amplifier to drive the output power stage. The designed PA delivered an output power of 13.86 dBm with a power-added efficiency (PAE) of 20% and a power gain of 26.66 dB.

#### I. Introduction

The growing demands for high throughput in wireless local area networks (WLANs) has generated increasing interest in the IEEE 802.11a [1] standards. This protocol provides data rates up to 54Mb/s using a 20-MHz channel bandwidth in the 5-GHz unlicensed national information infrastructure (UNII) hand.

Wireless transmitters often utilize power amplifiers  $(PA_S)$  as the final amplification stage. Together with the high gain provided, the nonlinear  $PA_S$  also cause distortions to the input signal both in-hand and out-of-hand, which have serious impact on the communication quality. Therefore, accurate PA modeling is needed to help troubleshoot the impairments and optimize the trade-off between the efficiency and nonlinearity [2]. A tradeoff exists between efficiency and linearity in conventional switching PAs and conducting PAs. Switching PAs, such as class-D, -E, and -F are very efficient, but highly non-linear [3]. On the other hand, conducting PAs, such as class-A, -B, and -C are highly linear but are very inefficient [4].

This work investigates the feasibility of designing a class-E PA with a high gain pre-amplifier to achieve high efficient and high PAE for WLAN system. Section III presents the designed PA and points out the main design problems. Section IV presents the simulation results of the proposed PA and final conclusions are given in section V.

G. C. Lin and Z. M. Lin are with the Graduate Institute of Integrated Circuit Design, National Changhua University of Education, Changhua, Taiwan, R.O.C.

E-mail: zmlin@cc.ncue.edu.tw

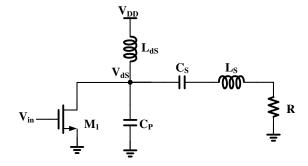

Fig. 1. A basic class-E stage.

#### II. CLASS-E OPERATION

Fig. 1 shows a class-E PA stage. The active device operates as a switch. The input signal Vin toggles the switch periodically with approximately 50% duty cycle. When the switch  $M_1$  is on, a linearly increasing current is built up through the inductor L<sub>dS</sub>. At the moment M<sub>1</sub> is turned off, this current is steered into the capacitor C<sub>P</sub>, causing the voltage across the switch  $V_{ds}$  to rise. The tuned network is designed such that in steady state, V<sub>dS</sub> returns to zero with a zero slope, immediately before M<sub>1</sub> is turned on. C<sub>S</sub> and L<sub>S</sub> operates as the band-pass filter and selectively passes the fundamental component of  $V_{dS}$  to the load, creating a sinusoidal output that is synchronized in phase and frequency with the input. In addition, the switch voltage and the switch current are never simultaneously nonzero. Since the instantaneous power dissipation of the switch is the product of these two quantities, the switch is ideally lossless, and all the power from the dc supply is delivered to the radio-frequency output.

# III. CIRCUIT DESIGN

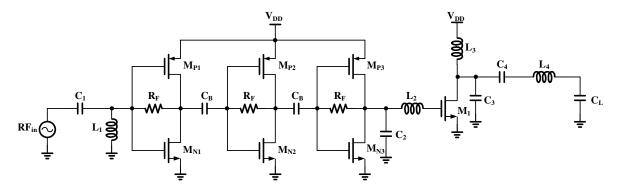

A schematic of the designed PA is shown in Fig. 2. The output stage of the power amplifier is a class-E amplifier, and the driver stage is a pre-amplifier that is composed of a cascaded class-D amplifier.

A class-E stage would require a square wave driving signal that the class-D [5] chains are used in order to meet the demand. In addition, a class-D amplifier has the highest gain when the biases of the input and output are set to the mid-point between  $V_{\rm DD}$  and the ground.

Fig. 2. Schematic of the designed PA

The input and the output of each class-D amplifier are connected through a feedback resistor  $R_{\rm F}$  in order to equalize the bias of the output to the bias of the input. To separate the bias of each class-D amplifier, class-D amplifiers are cascaded through dc blocking capacitors  $C_{\rm B}$ . By doing this, the gain degradation of each amplifier is prevented. As the output bias of the last class-D amplifier is used for the input bias of the power stage, no additional gate bias of the power transistors is needed. The transistor of each class-D amplifier is two times larger than that of the previous class-D amplifier and the size of the first one is set very small. Thus the gain of the power amplifier could be elevated.

The output stage used a traditional class-E amplifier. The size of  $M_1$  is designed as large as possible in order to obtain higher output power.

#### IV. SIMULATION RESULTS

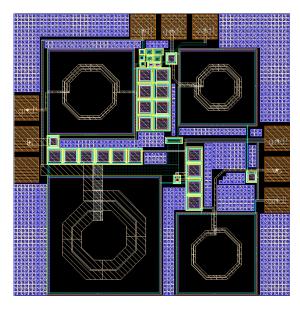

The performance of the PA was simulated using Advance Design System (ADS) software with 1.8V supply voltage in TMSC CMOS 0.18-µm technology. Fig. 3 shows the chip layout photograph of the PA.

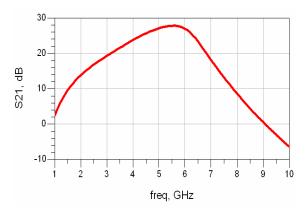

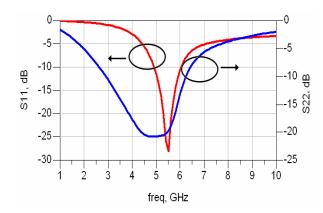

A small-signal gain of more than 27.5 dB is simulated at 5.8 GHz, as shown in Fig. 4. The input reflection coefficient S11 and output reflection coefficient S22 are better than -14 dB over the frequency band as shown in Fig. 5.

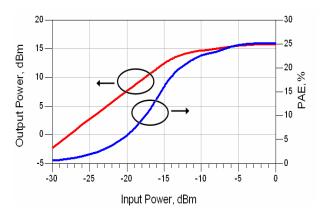

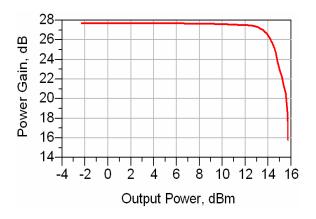

Fig. 6 shows the output power and PAE performance with a single-tone input signal. A 15.7 dBm saturated output power is achieved with a maximum PAE of 25.1%. As depicted in Fig. 7, the power gain and output power of  $P_{ldB}$  are 26.66 dB and 13.86 dBm, respectively. 20% PAE is achieved with that output power of  $P_{ldB}$  as shown in Fig. 8

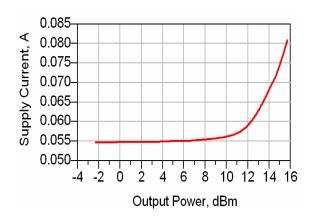

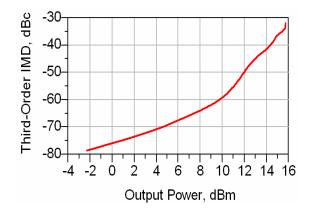

Fig. 9 exhibits the total current in accordance with an output power and the power amplifier uses a low quiescent current of Class AB mode in this work. The total current of 67 mA is achieved with the output power of  $P_{IdB}$ . As shown in Fig. 10, the simulated third-order IMD which is frequency-dependent distortion is less than -42 dBc for the frequency 5.8 GHz. Table I shows the summary of the performances compared with the reported works.

Fig. 3. Layout of the PA.

Fig. 4. Small-signal gain of the class-E power amplifier at  $V_{\rm DD}$ =1.8V.

Fig. 5. Input return loss and output return loss of the class-E power amplifier at  $V_{\rm DD}$ =1.8V.

Fig. 6. Output power and PAE versus input power.

Fig. 7. Power gain versus output power.

Fig. 8 PAE versus output power.

Fig. 9. Supply current versus output power.

Fig. 10. Third-order IMD corresponding to output power.

TABLE I COMPARISON OF PA PERFORMANCE

|                               | [6]     | [7]    | [8]     | This<br>work |

|-------------------------------|---------|--------|---------|--------------|

| Process                       | 0.18µm  | 0.18µm | 0.18µm  | 0.18µm       |

| Frequency(GHz)                | 5       | 1.95   | 5.85    | 5.8          |

| Supply<br>Voltage(V)          | 3.3     | 1.8    | 3.3     | 1.8          |

| Power Gain(dB)                | 25.5    | 15     | 18.5    | 26.66        |

| P <sub>out-1dB</sub> (dBm)    | 20.8    | 20     | 25      | 13.86        |

| PAE(%)                        | 26.7    | 42.2   | 20      | 20           |

| P <sub>diss</sub> (total)(mW) | 528     | 207    | 339.9   | 120.6        |

| Size(mm <sup>2</sup> )        | 1.1×2.2 | -      | 1.4×0.8 | 0.9×0.9      |

## V. CONCLUSION

A 5.8 GHz class-E CMOS PA fabricated in a TSMC 0.18um standard CMOS process with a cascaded class-D pre-amplifier for IEEE 802.11a WLAN application is presented. High gain and low quiescent current are achieved by using the cascaded class-D amplifier and the application of the proposed composition. A total power dissipation of 120.6 mW is consumed for an output power of 15.7 dBm with a maximum PAE of 25.1%. The power amplifier exhibits 26.66 dB power gain, 13.86 dBm  $P_{1dB}$ , and 20% PAE. The third-order IMD is less than -42 dBc with the output  $P_{1dB}$  for the frequency of 5.8 GHz.

### ACKNOWLEDGEMENT

This work was supported in part by the National Chip Implementation Center and by the National Science Council of Taiwan, R.O.C., under Grants 96-2221-E-018-024.

## REFERENCES

- [1] Wireless LAN Medium Access Control (MAC) and Phyxicul Layer (PHY) specifications: High-speed Physical Layer in the 5 GHz Bund, *IEEE Std* 802.11a-1999, Sept. 1999.

- [2] J. Liu, H. Arslan, L. P. Dunleavy, A. Webster, and J. Paviol, "Impact of carrier frequency dependent power amplifier behavior on 802.11a WLAN system,"

- European Conference on Wireless Technology, pp. 289 292, 2004.

- [3] Steve Cripps, RF Power Amplifiers for Wireless Communications, Artech House, 1999, pp. 47 50.

- [4] Behzad Razavi, RF Microelectronics, Prentice Hall, 1998, pp. 302 313.

- [5] J. Jang, C. Park, H. Kim, and S. Hong, "A CMOS RF Power Amplifier Using an Off-Chip Transmision Line Transformer with 62% PAE," *IEEE on Microwave and Wireless Components Letters*, vol. 17, pp. 385 – 387, May 2007.

- [6] H. Solar, R. Berenguer, I. Adin, U. Alvarado, and I. Cendoya, "A Fully Integrated 26.5 dBm CMOS Power Amplifier for IEEE 802.11a WLAN Standard with on-chip "power inductors"," IEEE MTT-S International on Microwave Symposium Digest, pp. 1875 1878, June 2006.

- [7] Ping-Chun Yeh, Kuei-Cheng Lin, C.Y.LEE\*, and Hwann-Kaeo Chiou., "A 1.8-v monolithic SiGe hbt power amplifier with a novel proposed linearizing bias circuit," 2004 IEEE Asia-Pacific Conference on Circuits and Systems, pp. 305 308, December 2004.

- [8] J. H. Kim, Y. S. Noh, and C. S. Park, "A low quiescent current 3.3V operation linear MMIC power amplifier for 5 GHz WLAN applications," *IEEE MTT-S International on Microwave Symposium Digest*, pp. 867 – 870, June 2003.